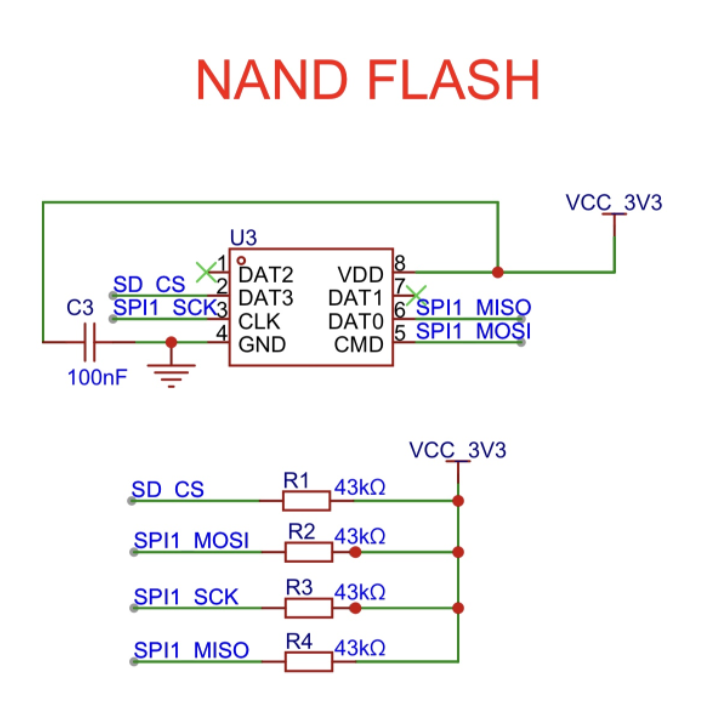

问题描述:主控型号是stm32l496,这一部分电阻没用你们给的10k用的43k,这个我找别人测试 说是通信没通上,硬件电路问题么,总线没响应,我有点没懂就是spi通信不上!

问题分析:针对SPI通信问题,结合电阻值更换的情况,以下是可能的原因及解决步骤:

上拉/下拉电阻:若43k电阻用于SPI信号线(SCK、MOSI、MISO、CS)的上拉或下拉:

问题:43k阻值过大,可能导致信号边沿(上升/下降时间)过慢,尤其在高速SPI模式下无法满足时序要求。

建议:SPI通常需要较强驱动能力,上拉电阻推荐4.7k~10k。尝试换回10k电阻或选择更小阻值。

分压/限流电阻:若电阻用于其他用途(如电平转换、分压供电),需验证分压后电压是否满足从设备需求。

信号完整性测试:

信号幅值是否达标(如3.3V或5V)。

上升/下降时间是否过快或过慢(通常应 < 10%时钟周期)。

是否存在噪声或畸变。

用示波器测量SCK、MOSI、CS信号波形,检查:

连接检查:

确认SPI线路(SCK、MOSI、MISO、CS)无短路、断路或虚焊。

确保从设备电源稳定,地线连接良好。

片选信号(CS):

检查CS引脚是否在通信时被正确拉低/释放。

确认CS信号是否因电阻值改变导致电平异常。

SPI参数匹配:

检查STM32的SPI配置(时钟频率、CPOL、CPHA)是否与从设备要求一致。

降低时钟频率(如从10MHz降至1MHz),测试是否因电阻导致高速通信失败。

GPIO模式:

确认SPI引脚配置为正确的复用功能模式(AF模式),非普通GPIO。

验证推挽输出(PP)或开漏(OD)模式是否适用当前电路。

换回10k电阻:临时替换为原10k电阻,测试通信是否恢复,以确认是否为电阻值问题。

最小系统测试:断开无关外设,仅保留SPI主从设备,排除其他干扰。

从设备初始化:确保从设备已正确上电并初始化(如需要配置寄存器)。

中断冲突:检查是否有中断信号未正确处理,导致通信流程阻塞。

ESD/过压损坏:若更换电阻前曾带电操作,检查芯片或从设备是否损坏。

电阻值替换影响:

信号边沿变缓:43k阻值过大,上升/下降时间延长,无法满足高速SPI时序要求。

驱动能力不足:高阻值上拉可能导致信号电平无法快速切换,尤其在长走线或高容性负载时。

若将SPI信号线(如SCK、MOSI、CS)的上拉电阻从10k改为43k,可能导致:

文件内容分析:

您提供的文件包含大量电阻列表(如R1~R500+),但缺少具体连接信息,无法直接关联到SPI线路。

存在重复电阻编号(如R553)、格式混乱,需确认电路图的准确性。

硬件检查:

使用示波器测量SCK、MOSI、CS波形,观察上升/下降时间是否在允许范围内(通常需小于时钟周期的10%)。

检查信号幅值(3.3V或匹配从设备电平)。

确认电阻位置:找到SPI总线(SCK、MOSI、MISO、CS)上的电阻,检查是否为上拉/下拉电阻。

替换回10k电阻:临时换回原设计值,测试通信是否恢复,以验证是否为电阻值问题。

检查信号完整性:

电路连接验证:

确保SPI引脚连接正确(主从设备的SCK、MOSI、MISO交叉连接,CS独立控制)。

检查NAND Flash的电源(VCC_3V3)和地(GND)是否稳定,避免电压跌落。

软件配置:

降低SPI时钟频率:尝试将时钟从高频(如10MHz)降至低频(1MHz),观察是否因电阻导致高速通信失败。

匹配CPOL/CPHA:确保STM32与NAND Flash的时钟极性和相位配置一致。

GPIO模式:确认SPI引脚配置为复用功能模式(AF),非普通GPIO。

排查其他可能性:

虚焊或短路:检查SPI线路和电阻焊点是否接触良好。

从设备损坏:尝试更换NAND Flash芯片,排除硬件损坏可能。

提供完整电路图:若电阻列表无法明确关联SPI线路,需提供具体的SPI相关电路部分,尤其是电阻连接方式。

检查NAND Flash初始化:确保从设备已正确初始化(如发送复位命令、配置寄存器)。

ESD防护:检查是否因静电放电导致芯片损坏。

根本原因可能是43k电阻导致信号时序不满足要求。建议优先换回10k电阻并测试信号波形,同时验证软件配置。

电话:176-6539-0767

Q Q:135-0379-986

邮箱:xcz@xczmemory.cn

地址:深圳市联创商务中心13层1308室