SD NAND的硬件接口设计是嵌入式系统中确保存储模块稳定运行的关键。其接口通常遵循SD卡协议标准,但在物理封装、引脚定义和信号处理上有独特要求。以下是SD NAND硬件接口的核心要点解析:

核心引脚:

CLK:时钟信号(主机控制,频率最高50MHz)

CMD:双向命令/响应线(初始化和数据传输控制)

DAT0-DAT3:4位双向数据总线(高速模式下同步传输)

VCC/GND:3.3V供电(典型电流需求200mA)

优势:

传输速率高(理论可达50MB/s)

支持热插拔(需硬件设计配合)

核心引脚:

CS:片选信号(低电平有效)

MOSI:主机输出从机输入

MISO:主机输入从机输出

SCK:时钟信号(由主机控制)

适用场景:

MCU资源有限(如无专用SDIO控制器)

低速应用(SPI模式速率通常低于25MHz)

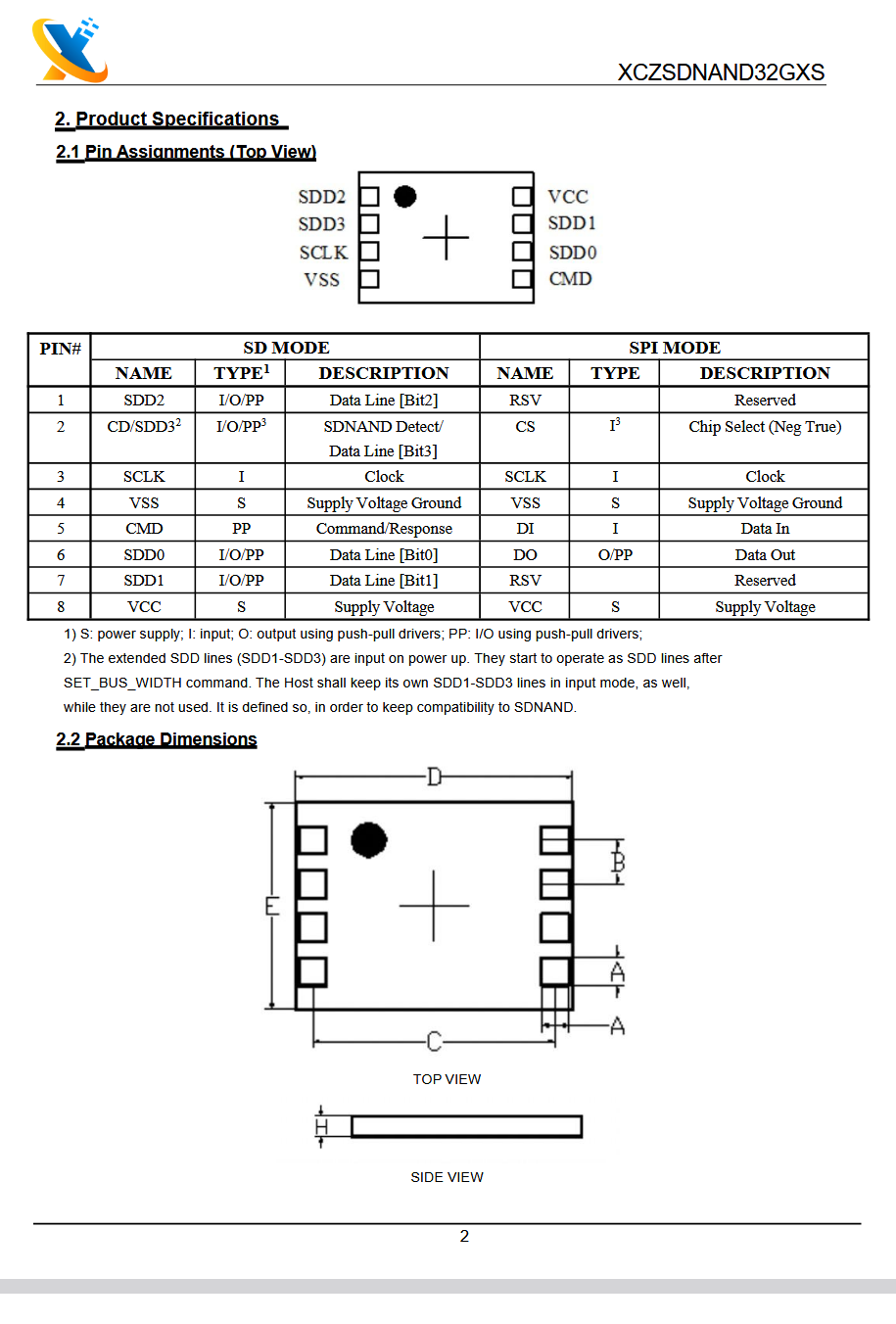

LGA-8(Land Grid Array):

尺寸:常见6×8mm或6.6×8mm

焊盘布局:8个焊盘分布于芯片底部,无引脚凸起

典型引脚定义示例(以某型号为例):

| 焊盘编号 | 功能 | 说明 |

|---|---|---|

| 1 | DAT2 | 数据线2(SDIO模式) |

| 2 | DAT3/CS | 数据线3或SPI片选 |

| 3 | CMD/DI | 命令线或SPI数据输入 |

| 4 | VCC | 3.3V电源 |

| 5 | CLK/SCK | 时钟信号 |

| 6 | GND | 地线 |

| 7 | DAT0/DO | 数据线0或SPI数据输出 |

| 8 | DAT1/IRQ | 数据线1或中断信号 |

特殊封装:

部分工业级型号采用WSON封装(带散热焊盘)

引脚映射对比:

VCC/GND:电源引脚位置差异可能导致短路

DAT3与CS:SDIO/SPI模式复用引脚定义可能不同

需核对不同厂家的Pinout图,重点关注以下信号:

封装适配:

焊盘尺寸误差需≤0.05mm(LGA封装对PCB加工精度要求高)

供电要求:

电压:2.7V-3.6V(推荐3.3V±5%)

电流:峰值电流≥200mA(写入操作时瞬时需求)

滤波设计:

必选:在VCC引脚附近添加0.1μF陶瓷电容(抑制高频噪声)

推荐:并联10μF钽电容(应对电流突变)

上拉电阻:

CMD和DAT线需接4.7kΩ上拉电阻(部分MCU内部集成)

SPI模式的CS线建议增加10kΩ上拉

布线规则:

CLK线长度≤50mm,且远离高频信号(如WiFi天线)

数据线等长误差控制在±5mil以内(SDIO高速模式必需)

敏感信号线采用包地处理(两侧铺设GND铜皮)

回流焊参数:

无铅工艺:峰值温度235-245℃,持续时间60-90秒

有铅工艺:峰值温度215-225℃,持续时间30-60秒

虚焊预防:

焊盘设计开窗面积≥80%

使用氮气保护焊接(减少氧化)

排查步骤:

测量VCC电压是否稳定(3.3V±5%)

检查CLK信号是否存在(示波器观测50MHz方波)

验证CMD线上拉电阻是否遗漏

案例:

某设计中因DAT3引脚未正确配置为SPI片选(CS),导致模式冲突

常见原因:

CLK信号串扰(未做包地处理)

电源纹波过大(滤波电容容值不足)

解决:

在CLK线两侧铺设地线

增加22μF电解电容并联滤波

接口兼容性优先:

选择支持SPI/SDIO双模式的型号(如芯存者全系列)

确认封装与现有PCB工艺匹配(LGA-8需高精度贴片机)

量产测试项:

电源波动测试(3.3V±10%)

4GB文件连续写入(验证长时间稳定性)

-40℃~85℃温度循环测试(工业级应用必需)

SD NAND的硬件接口设计需紧扣三大核心:

协议适配:明确SDIO/SPI模式下的引脚复用规则

物理匹配:严格遵循LGA封装的焊接与PCB设计要求

信号质量:从电源滤波到等长布线全程把控

建议首次设计时直接采用厂商参考设计,可规避80%以上的硬件兼容性问题。量产阶段需重点关注焊接良率和环境适应性测试。

电话:176-6539-0767

Q Q:135-0379-986

邮箱:xcz@xczmemory.cn

地址:深圳市联创商务中心13层1308室