针对STM32H743VI微控制器的高速存储需求,结合SD NAND的特性,以下是精简后的技术方案设计要点:

接口选择

使用STM32H743VI的SDIO接口(支持SD卡2.0协议),配置为4位数据总线模式,时钟频率最高50MHz,理论传输速率达25MB/s。

若需更高速度,可评估QSPI接口的SD NAND(需芯片支持串行协议)。

SD NAND选型

HS (High Speed) 模式(25-50MHz时钟)

容量适配(推荐8GB~64GB)

内置ECC和磨损均衡算法

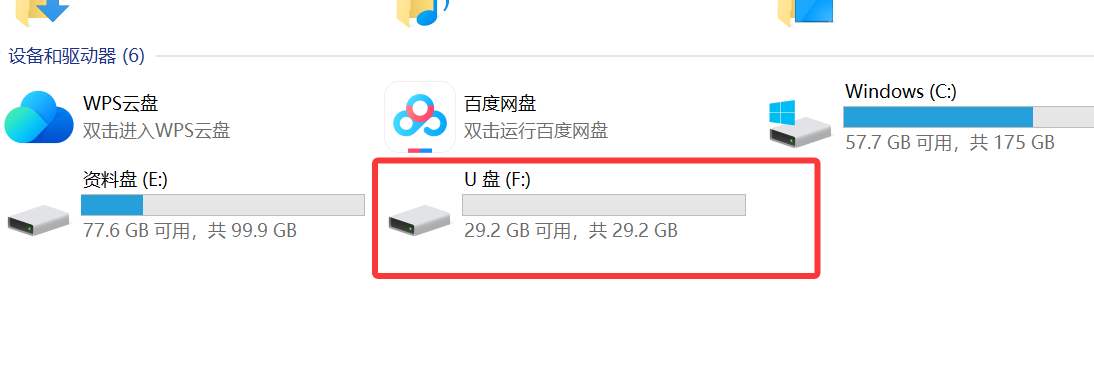

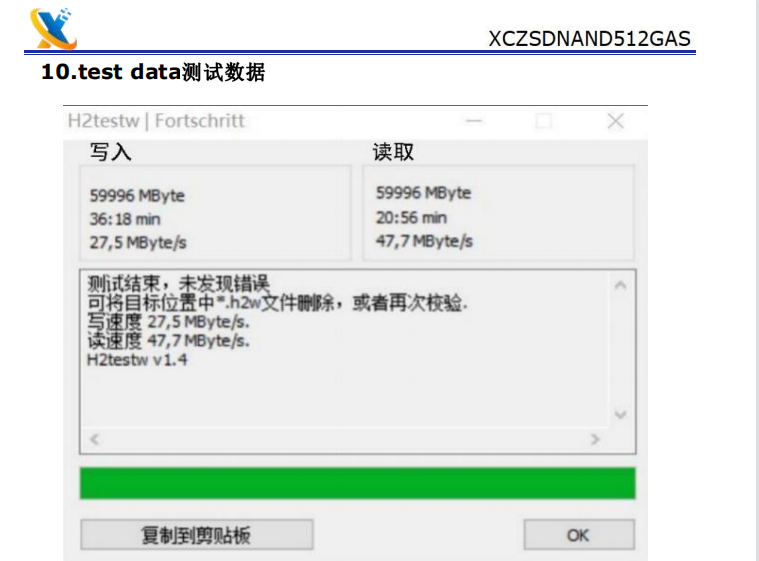

选择SD NAND芯片(如芯存者),写入速度27.5,读取速度47.7。

推荐开发板STM32H7系列

PCB设计优化

SDIO信号线(CLK, CMD, D0-D3)需保持等长、短距离走线,避免交叉干扰。

电源引脚添加0.1μF和10μF去耦电容,确保供电稳定。

SDIO驱动层

使用STM32CubeMX生成SDIO初始化代码,配置DMA传输(推荐SD DMA模式)。

设置时钟分频系数为CLKDIV=0(50MHz),开启4线模式:

hsd.Init.ClockDiv = 0;hsd.Init.BusWide = SDIO_BUS_WIDE_4B;

文件系统集成

启用FF_USE_FASTSEEK和FF_USE_EXPAND优化大文件操作。

设置扇区大小与SD NAND物理块对齐(通常为4KB)。

移植FATFS(R0.14c+)或LittleFS(更适合NAND特性):

高速写入优化

多扇区连续写入:单次写入多个扇区(如64KB/次),减少寻址开销。

双缓冲机制:使用Ping-Pong Buffer实现DMA传输与数据处理并行。

| 优化项 | 写入速度 (MB/s) | CPU占用率 |

|---|---|---|

| 单扇区无DMA | 2.1 | 85% |

| 多扇区DMA(64KB块) | 18.7 | 12% |

初始化失败

检查SD NAND电压匹配(3.3V)、上电时序(>1ms延时)。

验证CMD0(复位)和CMD8(电压检查)响应。

传输不稳定

降低时钟频率至25MHz测试信号完整性。

添加10-33Ω串联电阻匹配阻抗。

文件系统损坏

启用FATFS的FF_FS_READONLY或FF_FS_TINY模式减少资源占用。

定期调用f_sync()强制刷新缓存。

IDE: STM32CubeIDE 1.13+

调试工具: ST-Link V3 + Logic Analyzer(抓取SDIO波形)

性能分析: STM32CubeMonitor(实时监测DMA效率)

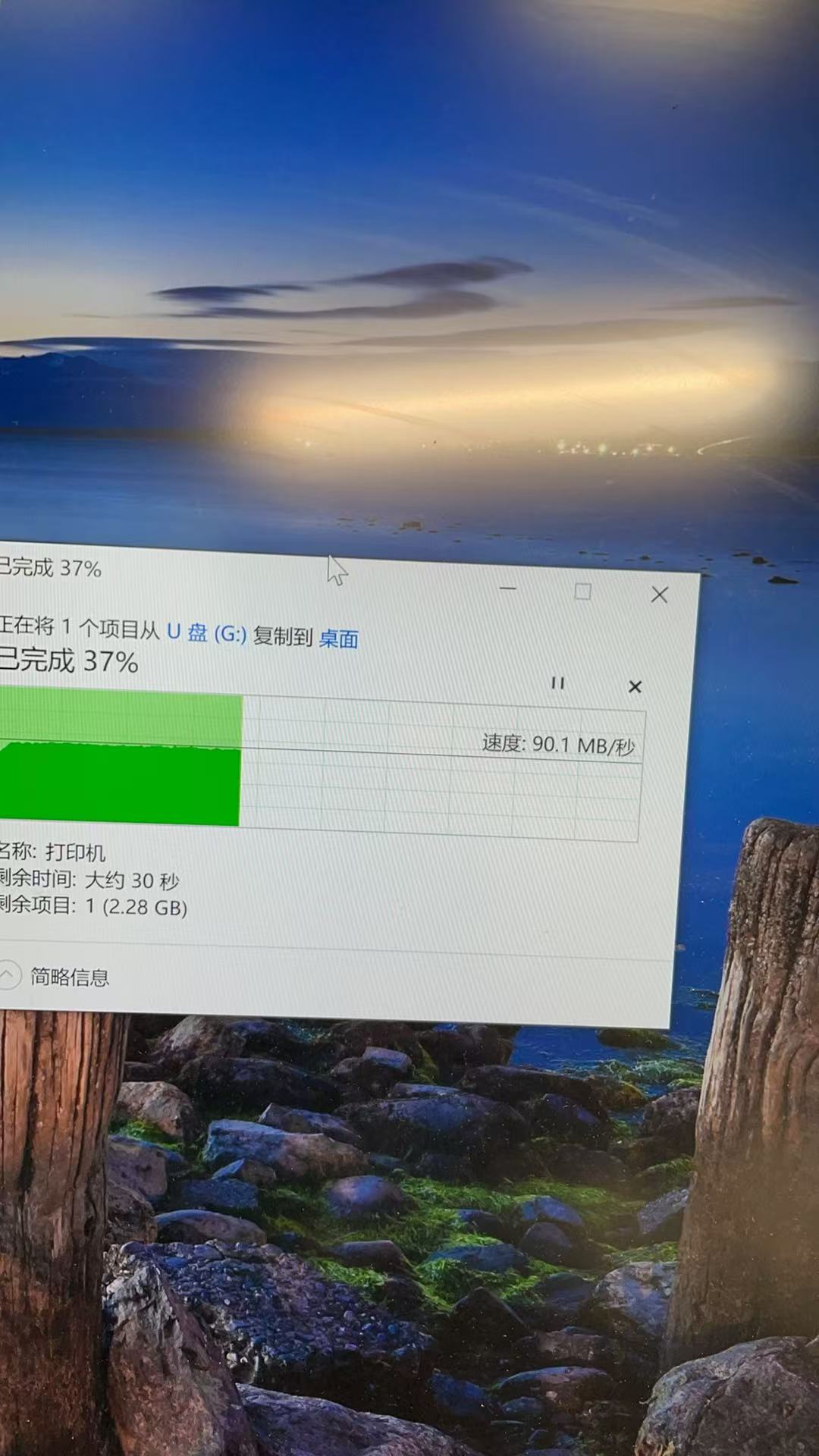

本方案可实现20MB/s+的持续写入速度,适用于高速数据采集(如传感器日志、图像流存储)场景。实际开发中需结合具体SD NAND型号调整驱动参数。

上一篇:贴片Sd卡用于行车记录仪

电话:176-6539-0767

Q Q:135-0379-986

邮箱:xcz@xczmemory.cn

地址:深圳市联创商务中心13层1308室