SD NAND的SD模式6线(CLK/CMD/DAT0-3) 是遵循SD卡物理层标准的全功能接口,专为高速数据传输和协议完整性设计。以下是深度解析:

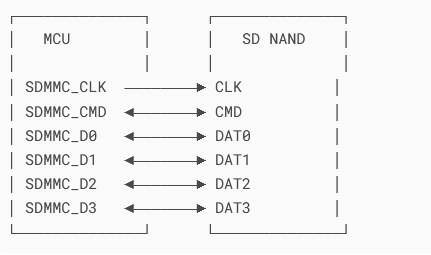

| 引脚 | 名称 | 方向 | 核心作用 |

|---|---|---|---|

| CLK | Clock | 主控→SD NAND | 同步时钟(50MHz+),控制所有指令/数据的传输节奏 |

| CMD | Command | 双向 | 传输指令(主控→设备)和响应(设备→主控)的专用通道 |

| DAT0 | Data Line 0 | 双向 | 默认数据线(单线模式),或4线并行传输的LSB |

| DAT1 | Data Line 1 | 双向 | 4线模式的数据线1,或用于中断检测(非传输时) |

| DAT2 | Data Line 2 | 双向 | 4线模式的数据线2 |

| DAT3 | Data Line 3 | 双向 | 4线模式的数据线3,兼作片选信号(上电初始化期间) |

关键特性:

DAT0-3支持并行传输 → 吞吐量可达104MB/s(UHS-I模式)

CMD线复用指令/响应 → 减少引脚占用

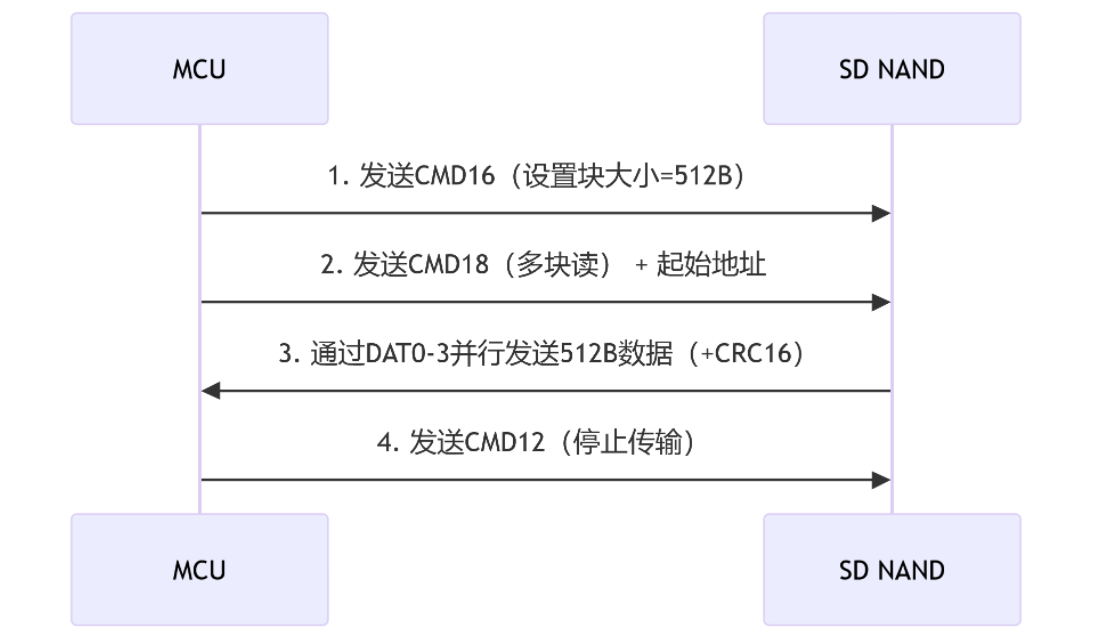

4线并行模式:DAT0-3同时传输数据(SPI模式仅单线MISO)

单线模式:1bit/时钟周期 → 理论25MB/s(50MHz时钟)4线模式:4bit/时钟周期 → 理论100MB/s(50MHz时钟)

支持高速协议:SDR25(50MHz),DDR50(双沿采样),UHS-I(104MB/s)

执行复杂指令(如ACMD41初始化协商电压)

错误重传机制(通过CMD17/18/24等指令控制)

块传输优化:单次读写512B~128KB(SPI模式需多次拆包)

可直接接入标准读卡器(如PC的SD插槽)

兼容Linux/Android等系统的SD Host Controller驱动

关键点:

DAT3在初始化阶段需保持高电平(作为片选)

每512B数据包尾附带16位CRC校验码(SPI模式无此机制)

| 特性 | SD 6线模式 | SPI 4线模式 |

|---|---|---|

| 协议复杂度 | 高(支持100+条SD指令) | 低(仅20+条SPI指令) |

| 峰值吞吐量 | 104MB/s(UHS-I) | 12.5MB/s(50MHz单线) |

| 硬件资源占用 | 需专用SDIO控制器(如STM32 SDMMC) | 通用SPI接口即可 |

| 错误处理 | 硬件CRC校验+自动重传 | 依赖软件校验 |

| 功耗 | 较高(4线激活) | 较低(按需唤醒) |

阻抗匹配(高速模式必须)

DAT0-3需做50Ω差分阻抗控制(长度差≤0.1mm)

CLK线包地处理(防止干扰数据线)

上电初始化电路

DAT3引脚接10kΩ上拉电阻(标识为SPI模式禁用)

VCC与CLK间加RC滤波(0.1μF电容+100Ω电阻防浪涌)

PCB布局规范

走线长度≤30mm,避免直角转弯(用45°或弧线)

4K摄像头:高速写入RAW图像数据(依赖4线并行)

工业PLC:毫秒级保存传感器日志(块传输效率优势)

车载娱乐系统:播放高清视频(需UHS-I带宽)

Linux嵌入式设备:通过SDIO接口挂载为系统磁盘

迁移提示:

若从SPI模式切换到SD模式:

硬件需重新布线(增加DAT1-3和CMD线)

软件重写驱动(调用SD协议栈如FatFs + SDIO HAL库)

为高性能存储而生的工业级接口:

✅ CLK = 超高速引擎

✅ CMD = 精准指令通道

✅ DAT0-3 = 4倍数据带宽

掌握其并行传输机制,即可释放SD NAND的完整性能!

电话:176-6539-0767

Q Q:135-0379-986

邮箱:xcz@xczmemory.cn

地址:深圳市联创商务中心13层1308室