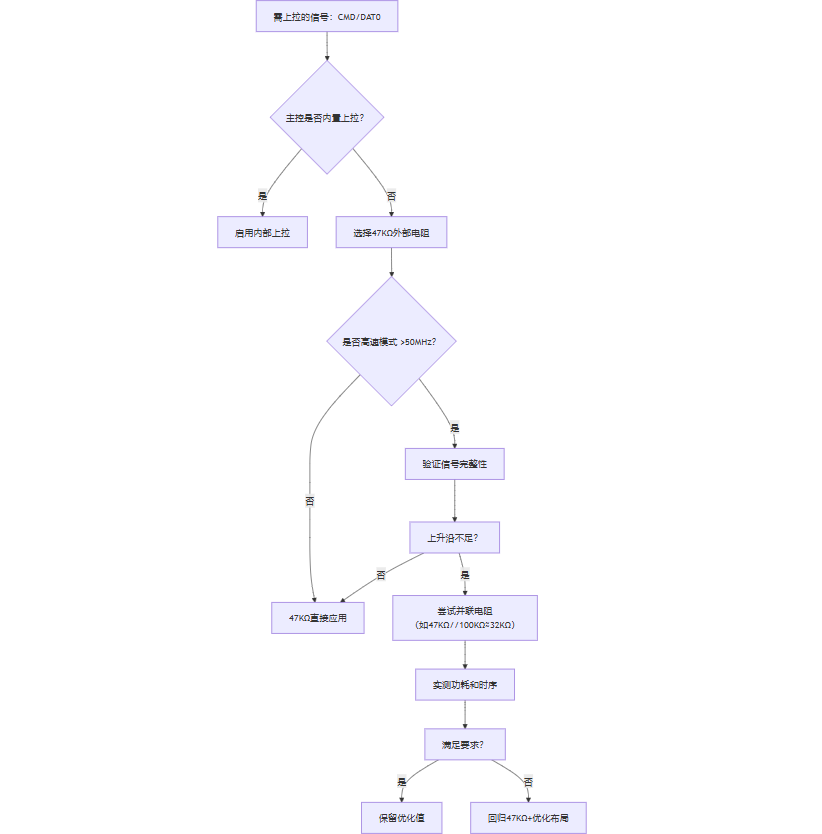

在SDIO总线设计中,4.7KΩ上拉电阻在特定条件下可以使用,但需谨慎评估其适用性。以下是关键分析:

通常不推荐:标准SDIO设计优先选择 10KΩ~100KΩ(典型值47KΩ),4.7KΩ属于偏小阻值。

潜在风险:

功耗增加:低阻值导致信号拉低时电流过大(例如3.3V系统:I = 3.3V / 4.7KΩ ≈ 0.7mA),可能超出主控IO驱动能力。

信号边沿变缓:过强的上拉会减缓下降沿速度,影响高速信号完整性。

总线冲突风险:多设备场景下可能引发驱动冲突。

| 场景 | 说明 |

|---|---|

| 1. 长走线或高干扰环境 | 低阻值增强抗干扰能力(如强电磁干扰环境),但需同步优化阻抗匹配。 |

| 2. 主控驱动能力极强 | 需确认主控IO可承受≥5mA拉电流(查阅芯片手册的I_OL参数)。 |

| 3. 超高速通信调试 | 临时用于改善上升沿(牺牲功耗),但需最终回归标准设计。 |

CMD/DAT0线:首选 47KΩ(平衡功耗与信号质量)。

CLK线:无需上拉(推挽输出)。

VDD检测线(CD/DAT3):若需上拉,用10KΩ~100KΩ。

- **主控IO驱动能力**:确保`I_OL(max) > VDD / Rp`(例:3.3V系统需满足`I_OL > 3.3V/4.7KΩ ≈ 0.7mA`)。- **信号上升时间**:用示波器测量是否满足SDIO时序(如SD模式50MHz要求上升沿<7ns)。- **功耗预算**:计算多信号线上拉的总电流(4线DAT+CMD用4.7KΩ时总电流≈3.5mA)。

分段上拉:主控端用47KΩ标准电阻 + 卡座端预留并联焊盘(调试时可选并4.7KΩ)。

集成上拉:启用主控内部上拉(多数现代SoC支持可编程上拉,阻值≈40KΩ~100KΩ)。

SD物理层规范:要求上拉电阻确保空闲状态高电平,但未指定阻值(依赖主控驱动特性)。

主控芯片手册:如STM32的SDIO外设要求最大上拉电流≤8mA(ST AN4767)。

实测案例:

Raspberry Pi SD卡接口:使用47KΩ(官方设计)。

某4G模块SDIO:要求外部10KΩ上拉(Quectel EC25设计指南)。

最终建议:若无特殊需求,坚持47KΩ;若必须用4.7KΩ,需提供额外设计证据(驱动能力计算、眼图测试报告)。高速信号(如SDIO 3.0 @200MHz)建议咨询原厂支持。

下一篇:sd nand命令详细配置

电话:176-6539-0767

Q Q:135-0379-986

邮箱:xcz@xczmemory.cn

地址:深圳市联创商务中心13层1308室